- 您现在的位置:买卖IC网 > Sheet目录2007 > MAX11040GUU+T (Maxim Integrated Products)IC ADC 24BIT 4CH 38-TSSOP

MAX11040K/MAX11060

24-/16-Bit, 4-Channel, Simultaneous-Sampling,

Cascadable, Sigma-Delta ADCs

23

Maxim Integrated

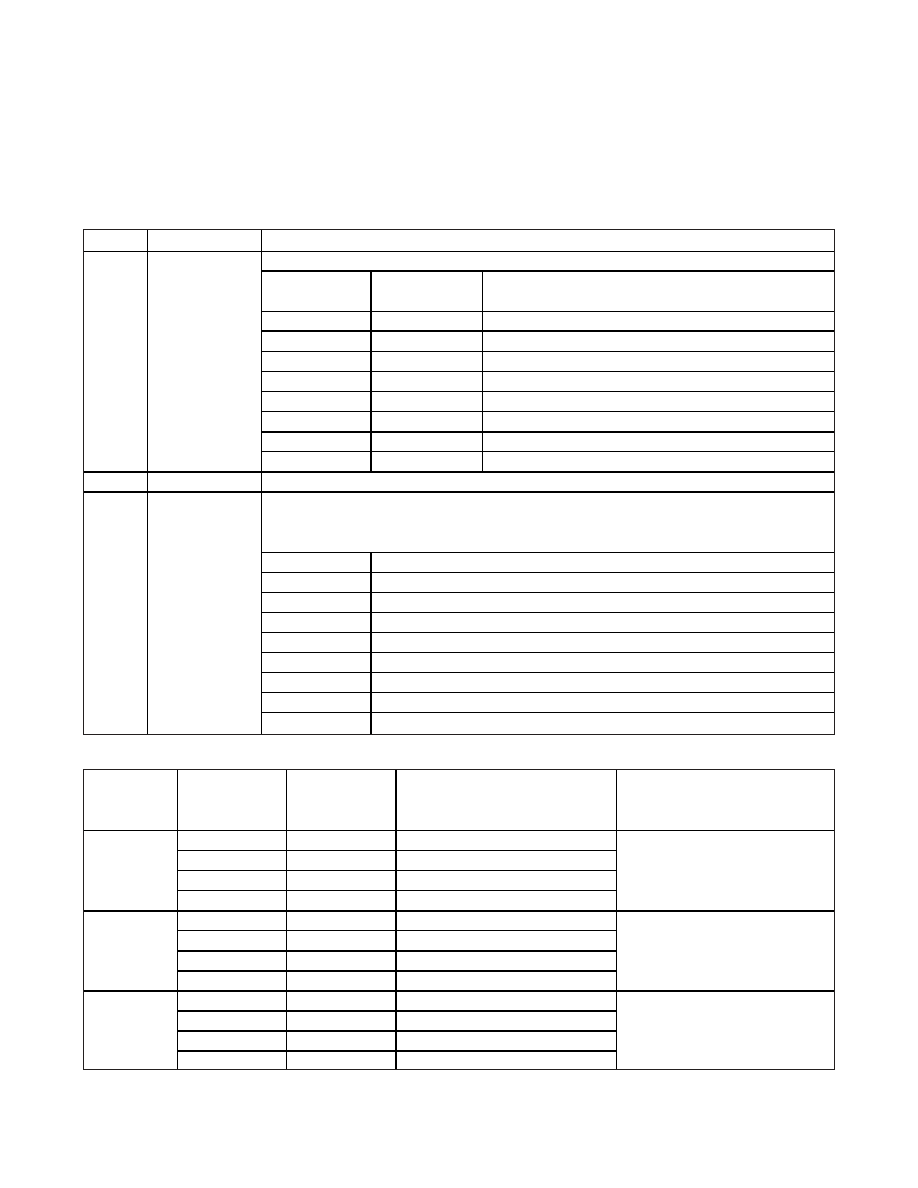

Table 8. Data-Rate Control Register

BITS

NAME

DESCRIPTION

Output data rate coarse adjust bits. FSAMPC[2:0] sets the coarse cycle factor.

FSAMPC

Coarse Cycle

Factor

Sample Rate in ksps

(fXIN CLOCK = 24.576MHz)

000

4

16

001

128

0.5

010

64

1

011

32

2

100

16

4

101

8

110

2

32

[15:13]

FSAMPC[2:0]

111

1

64

[12:11]

Reserved

Set to 0.

Output data rate fine adjusts bits. FSAMPF[10:0] increases the output data period by a number of

XIN clock cycles. This number is the value of the register times the fine cycle factor. Values of

FSAMPF greater than 1535 have no additional effect.

FSAMPC

XIN Fine Cycle Factor

000

1 cycle

001

32 cycles

010

16 cycles

011

8 cycles

100

4 cycles

101

2 cycles

110

1 cycle

[10:0]

FSAMPF[10:0]

111

1 cycle

Table 9. Examples of Output Data Rate as a Function of FSAMPC[2:0] and FSAMPF[10:0]

FSAMPC[2:0]

FSAMPF[10:0]

OUTPUT DATA

RATE (sps)

OUTPUT DATA PERIOD

(24.576MHz CLOCK CYCLES)

FSAMPF OUTPUT DATA PERIOD

RESOLUTION

(24.576MHz CLOCK CYCLES)

11xxxxxxxxx

250.1

98272

10111111111

250.1

98272

00000000001

499.7

49184

001

00000000000

500.0

49152

32

11xxxxxxxxx

500.2

49136

10111111111

500.2

49136

00000000001

999.3

24592

010

00000000000

1000.0

24576

16

11xxxxxxxxx

1000.3

24568

10111111111

1000.3

24568

00000000001

1998.7

12296

011

00000000000

2000.0

12288

8

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX11046ECB+T

IC ADC 16BIT PAR 250KSPS 64TQFP

MAX11046ETN+T

ADC 16BIT SAMPLING 8CH 56-TQFN

MAX11049ECB+

IC ADC 16BIT PAR 250KSPS 64TQFP

MAX1104EUA+

IC CODEC 8BIT 8-UMAX

MAX11100EUB+

IC ADC 16BIT SRL 200KSPS 10UMAX

MAX11101EUB+

IC ADC 14BIT SRL 200KSPS 10UMAX

MAX11102AUB+

IC ADC 12BIT SPI/SRL 10UMAX-EP

MAX1111CPE+

IC ADC 8BIT LP 16-DIP

相关代理商/技术参数

MAX11040K

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:24-/16-Bit, 4-Channel, Simultaneous-Sampling, Cascadable, Sigma-Delta ADCs

MAX11040K_1111

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:24-/16-Bit, 4-Channel, Simultaneous-Sampling, Cascadable, Sigma-Delta ADCs

MAX11040K_12

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:MAX11040K Evaluation Kit/Daughterboard

MAX11040KDBEVKIT

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:MAX11040K Evaluation Kit/Daughterboard

MAX11040KDBEVKIT#

功能描述:数据转换 IC 开发工具 MAX5135/11040/11612 Eval Kit w/ FMC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

MAX11040KEVKIT

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:MAX11040K Evaluation Kit/Daughterboard

MAX11040KEVKIT#

功能描述:数据转换 IC 开发工具 MAX5135/11040/11612 Eval Kit w/ FMC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V

MAX11040KGUU

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:24-/16-Bit, 4-Channel, Simultaneous-Sampling, Cascadable, Sigma-Delta ADCs